### Quantified Boolean Logic

Extension of propositional logic with boolean quantifiers.

We write

$$\exists A \ F$$

as an abbreviation of  $F[A/0] \lor F[A/1]$

$$\forall A \ F$$

as an abbreviation of  $F[A/0] \land F[A/1]$

Abbreviations can be nested, and then they are "unfolded" inside-out:

$$\exists A \forall B \ (A \land B)$$

abbreviates

$$\exists A \ (A \lor 0) \land (A \lor 1)$$

which abbreviates

$$((0 \lor 0) \land (0 \lor 1)) \lor ((1 \lor 0) \land (1 \lor 1))$$

Intuitively,  $\exists A \forall B \ (A \land B)$  "means"

there exists a truth value for A such that for every truth value for B the formula  $(A \wedge B)$  becomes true.

### Modelling circuits with QBL

Gates as boolean formulas

Stable states as satisfying truth assignments

not and or xor

$$a - b \quad b \quad b - c \quad b - c \quad b - c$$

$$not(a, b) \quad \equiv \neg a \leftrightarrow b$$

$$and(a, b, c) \quad \equiv \quad (a \land b) \leftrightarrow c$$

$$or(a, b, c) \quad \equiv \quad (a \lor b) \leftrightarrow c$$

$$xor(a, b, c) \quad \equiv \quad ((\neg a \land b) \lor (a \land \neg b)) \leftrightarrow c$$

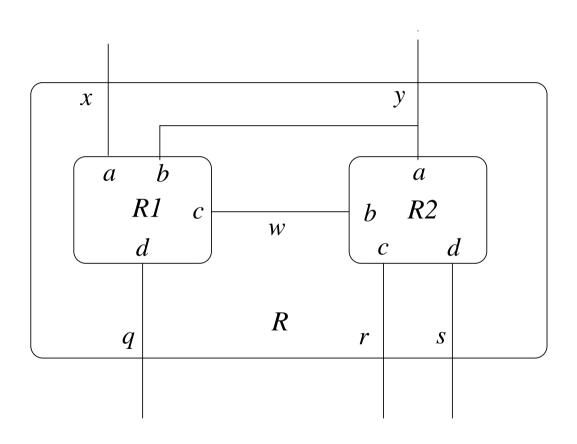

### Combining gates means combining formulas

Combine gates with  $\land$ ,  $\exists$  (and renaming of atomic formulas)

$$R(x, y, q, r, s) = \exists w \, R_1(x, y, w, q) \land R_2(y, w, r, s)$$

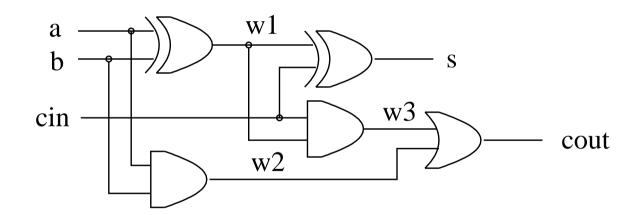

#### A full adder

$$\mathbf{full\_adder}(a, b, s, cin, cout) \equiv$$

$$\exists w_1 \exists w_2 \exists w_3 \ \mathbf{xor}(a, b, w_1) \land \mathbf{xor}(w_1, cin, s) \land \mathbf{and}(a, b, w_2) \land$$

$$\mathbf{and}(cin, w_1, w_3) \land \mathbf{or}(w_3, w_2, cout)$$

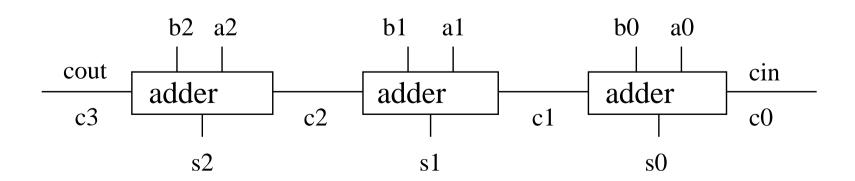

### A n-bit ripple-carry adder

$$c_{2}$$

$c_{1}$   $cin$   $(=0)$

$a_{2}$   $a_{1}$   $a_{0}$

$+$   $b_{2}$   $b_{1}$   $b_{0}$

$cout$   $s_{2}$   $s_{1}$   $s_{0}$

Wire together n 1-bit adders where i-th carry-out is i+1-st carry-in, first carry is the carry-in and last is the carry-out.

We obtain the formula

$$\mathbf{adder}_{n}(a_{0}, \dots, a_{n-1}, b_{0}, \dots, b_{n-1}, s_{0}, \dots, s_{n-1}, cin, cout) \equiv \exists c_{0} \exists c_{1} \dots \exists c_{n} (c_{0} \leftrightarrow cin) \land (c_{n} \leftrightarrow cout) \land \\ \bigwedge_{i=1}^{n-1} \mathbf{full\_adder}(a_{i}, b_{i}, s_{i}, c_{i}, c_{i+1}))$$

Problem: too slow. Each  $c_i$  can only be computed after all of  $c_{i-1}, \ldots, c_0$  have been computed

Delay: 2n + 2 time units for n-bit numbers

### A carry-look-ahead n-adder

Compute all of  $c_{n-1}, \ldots, c_0$  (and cout) concurrently

First step: given  $a_{n-1} \dots a_0$  and  $b_{n-1} \dots b_0$ , identify the positions  $i \in [0, n-1]$  that are

- Generating:  $c_{i+1} \equiv 1$  independently of  $c_i$ . These are the positions such that  $1 = g_i \equiv \text{and}(a_i, b_i)$ .

- Propagating:  $c_{i+1} \equiv c_i$ , i.e.,  $c_i$  is 'propagated' to  $c_{i+1}$ . These are the positions such that  $1 = p_i \equiv \mathbf{xor}(a_i, b_i)$

Observe: all  $g_i, p_i$  can be computed simultaneously

#### A carry-look-ahead n-adder

Second step: compute the  $c_i$ 's by

$$c_i \equiv g_i \vee (p_i \wedge g_{i-1}) \vee (p_i \wedge p_{i-1} \wedge g_{i-2}) \vee \ldots \vee (p_i \wedge p_{i-1} \wedge \ldots \wedge g_0)$$

Logarithmic delay in n using balanced  $\vee$ -trees and  $\wedge$ -trees.

Delay for 64 bits: 23-56 units (instead of 130)

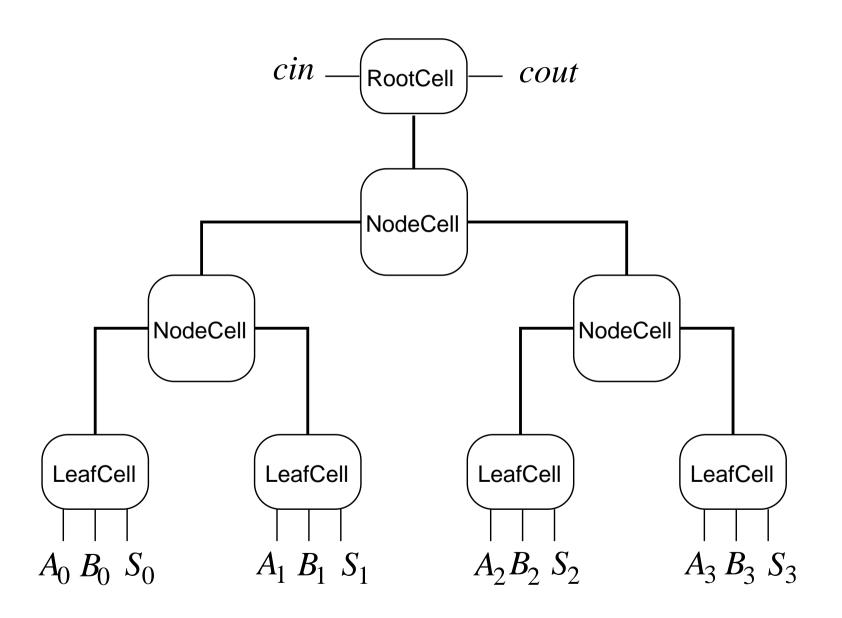

## Description of the circuit (for 4 bits)

# Description of the circuit II

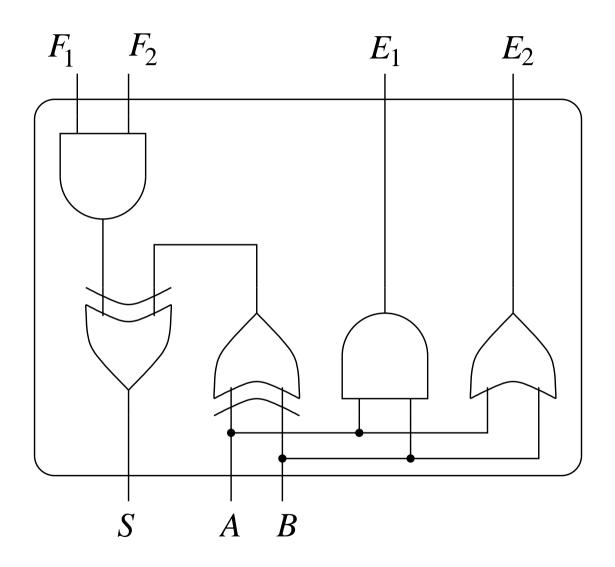

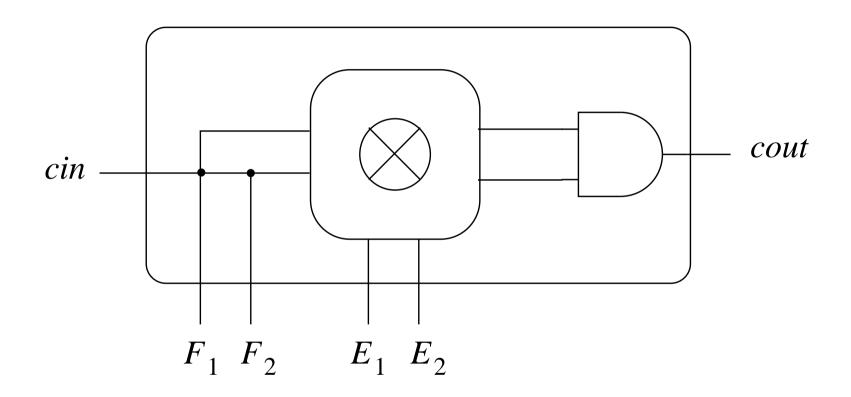

LeafCell circuit

# Description of the circuit III

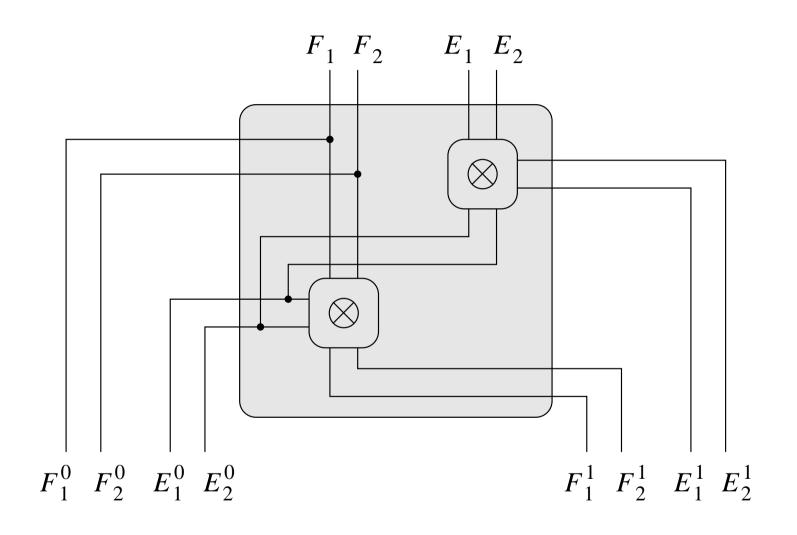

### Description of the circuit IV

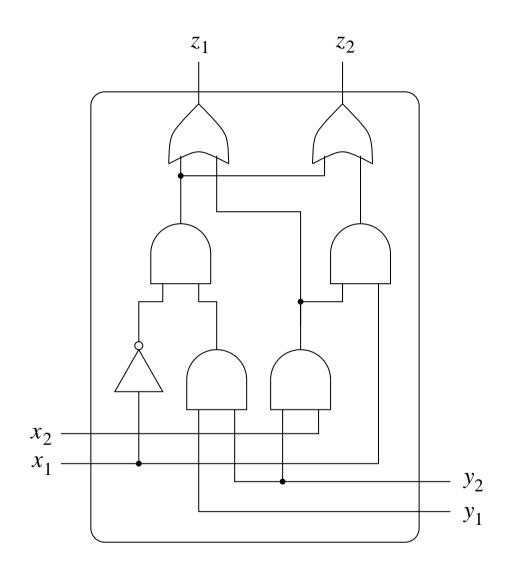

NodeCell circuit

# Description of the circuit V

RootCell circuit

#### Verification of the carry-look-ahead n-adder

Check validity of

$$\mathbf{adder}_{n}(a_{0}, \dots, a_{n-1}, b_{0}, \dots, b_{n-1}, s_{0}, \dots, s_{n-1}, cin, cout)$$

$$\Leftrightarrow$$

$$\mathbf{cla}_{n}(a_{0}, \dots, a_{n-1}, b_{0}, \dots, b_{n-1}, s_{0}, \dots, s_{n-1}, cin, cout)$$

Results of the SAT 2002 competition on a variant of this problem:

- Task was to compare 2, 4, 8, ..., 256 bits adders (8 problems)

- From 26 variables and 70 3CNF clauses to 4584 variables and 13226 clauses

- Fastest solver (Zchaff) checked all 8 problems in 14 seconds

- More info at www.satcompetition.org

Rule-of-thumb: circuits with some hundreds of gates are routinely solved